About the tutorials

About the tutorials:

SpeakHDL utilizes a

'teach by example'

approach to FPGA programming. Each of the tutorials are given as series of examples are are intended to be self explanatory and self contained. Each example is broken down into two short videos.

- SpeakHDL Design Video : Intended to familiarize the user with voice commands that can be used

- SpeakHDL Simulation Video : Intended to familiarize the user with how to simulate the design

The two videos will appear as clickable items similar to the items below and should be 'double clicked' and played in full screen mode.

Each example is intended to familiarize the user with a particular procedural operation that can be performed. The user is encouraged to watch the video try reproduce the simulation on their own results before moving on to the next example.

Background Information

Background Information:

Speak HDL utilizes native VHDL as the hardware description language. However, SpeakHDL

does

not

assume that the user is familiar with VHDL

in any way

. However, for uses that are familiar with VHDL and those interested in the architecture that is used to make procedural programming to work one should see:

- The Fixed Port Flat Architecture Design Pattern which shows the hardware architecture and design strategy

-

Architecture, Terminology and Definitions

that explains some terminology that is specific SpeakHDL and necessary to make a distinction between traditional VHDL programming

- How the Framework Module organizes its data structures which explains how the data is organized from a programming prospective

General Purpose Counter

Overview

Overview:

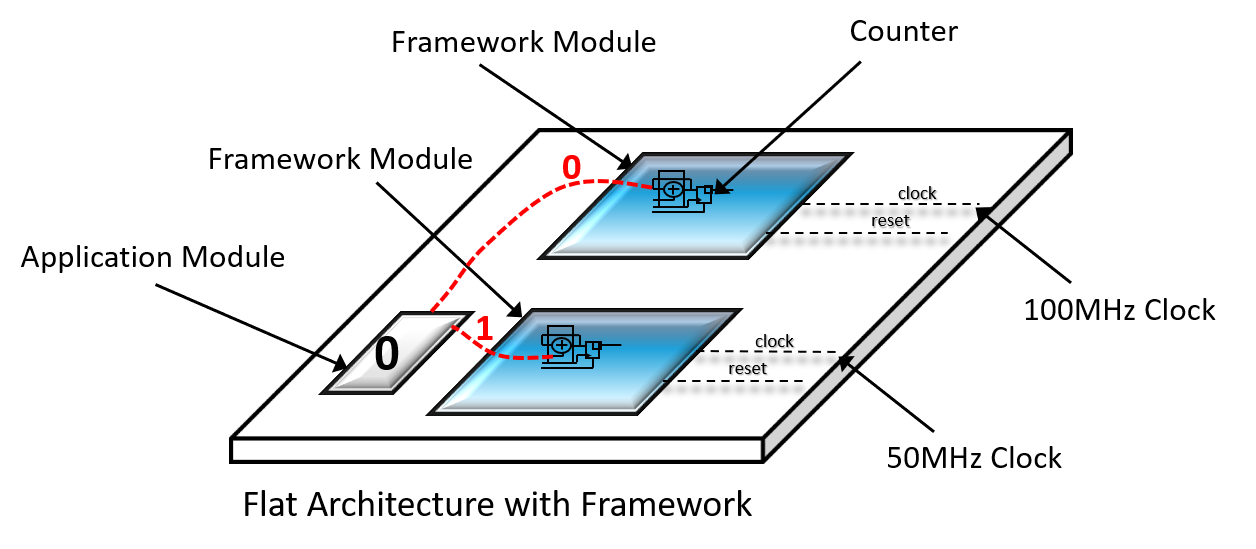

The general purpose counter is probably the most utilized

framework

component that can be configured by an API call. In order to request usage of a counter, an

application module

makes a call to the VHDL procedure CONFIGURE_COUNTER by speaking the commands "

configure counter

". Counters are enabled by default, and can be configured to operate on different clock domains extremely easily by voice commands.

Counters can be configured to count clock cycles or count signal edges simply by changing the type of the enable signal. In addition, counters can also be configured to trigger state machine transitions when they rollover

Example Requirements

Example Requirements:

- Create a file named count_module.vhd

- Create Two Counters on two separate clock domains

-

The faster counter should have

counter index 0

and should count to 20

(0 to 19)

on the system clock domain (100MHz).

-

The slower counter should have

counter index 1

and should count to 10

(0 to 9)

on a 50MHz clock domain.

Watch the Videos

Watch the Videos:

Tutorial lessons to be learned

Counters can be placed on different clock domains. There can be a number of counters on a single clock domain or they can be separated onto different clock domains. The user is free to assign any unused index to any counter. However, it is suggested that contiguous indexes are utilized to index counters.

example

Reviewing the Commands

- "restart from scratch"

- "configure counter zero"

- "count twenty"

This sequence of commands will generate a counter operating on the default system clock domain

(100MHz)

. The counter will increment from 0 to 19 on every clock cycle then rollover and repeat. The counter will asserting a done strobe every time it reaches 19.

Now we wish to add a second counter operating on a different clock domain. This sequence of commands will generate a counter (with counter index one) operating operating on a fifty-megahertz clock domain. That counter will count from 0 to 10 on ever clock cycle and rollover and repeat. The counter will asserting a done strobe every time it reaches 9.

- "resource one"

- "clock fifty-megaherz"

- "configure counter one

- "count ten"

- "ok".

When the command "ok" is spoken, SpeakHDL does calculations related to the number of resources that the application modules will be using.

Simulation Results

Simulation Results

The simulation shows the two counters behave as expected. This example chose 50MHz because it was exactly half of the system clock. With that being the case, counter zero increments twice a fast as counter one on the slower clock domain. As shown in the graphic, the done strobe of counter zero is half the pulse width of the done done strobe of counter 1.

VHDL Reference

VHDL Reference:

-

Completed Example:

counter_example.vhd

.

- API Syntax: CONFIGURE_COUNTER

See Also

See Also

-

CONFIGURE_COUNTER

- Item 2

- Item 3

- Item 4

Time Counter

Overview

Overview:

The time counter is composed of two counters chained together specifically used for counting time. The time counter can be used to create a hardware timeout, or pattern of output strobes at a specified time interval. As opposed to the general purpose counter, the time counter cannot be 'suspended' when the enable signal is '0'.Instead, the time counter is either running (counting time) when the enable signal is true or logic '1' or both counters are reset to zero when the enable is '0' or false.

An

application module

request requests the use of a time counter from the

framework module

when the user speaks the command

"time counter"

. This voice command creates the VHDL procedure call

TIME_COUNTER

which configures a time counter in its default configuration.

Example Requirements

Example Requirements:

- Create a Time Counter

- Configure the DIVIDE_COUNTER (faster counter) to strobe and rollover every 2.4 micro-seconds

- Configure the DELAY_COUNTER to to strobe at the 5th strobe of the DIVIDE_COUNTER

- Wire DELAY_COUNTER strobe (slower counter) to output pin 0 of the application module, and wire the DIVIDE_COUNTER strobe (faster counter) to output pin 1 of the application module.

Note: The total time delay would before the DELAY_COUNTER repeats would be 12 us (5 x 2.4 us).

Watch the Videos

Watch the Videos:

Tutorial lessons to be learned

When used specifically for counting time periods, the time counter is more easily setup than two general purpose counters. Both the DELAY_COUNTER and the DIVIDE_COUNTER can be configured to count individually, however, the typical use case is setting up the DIVIDE_COUNTER to strobe at a specified time interval (us, ms, or seconds), while the DELAY_COUNTER is set to an integer number of counts.

example

Reviewing the Commands

- "clear screen"

- "restart from scratch"

- "time count"

- "delay 5"

- "divide two point four micro-seconds"

The "

time count"

command creates the procedure call TIME_COUNT. Once the procedure is created, the "

delay

" command to used to select the delay parameter, and "divide" command command to select the divide parameter of the procedure call. The delay and divide command, can be performed in any order. After the parameter is selected, then the next words specify the argument to the parameter. The delay parameter being five, and divide parameter 2.4us.

- "signal output zero"

- "assign delay done"

- "signal output one"

- "assign divide done"

- "ok"

In the same manner, the command "

signal output

" is used to select a pin number. The next words "

delay done

" means to wire the delay done signal to the selected pin number (in this case output pin zero). The next commands "signal output one" selects pin one, then the "

assign divide done

", wires the divide done signal to output pin one.

Simulation Results

Simulation Results

"Sed ut perspiciatis unde omnis iste natus error sit voluptatem accusantium doloremque laudantium, totam rem aperiam, eaque ipsa quae ab illo inventore veritatis et quasi architecto beatae vitae dicta sunt explicabo.

VHDL Reference

VHDL Reference:

The competed counter example is shown in file XXX

_example.vhd

.

For API syntax see < ref>

See Also

See Also

State Machine Event Driven Transitions

Overview

Overview:

State machine time transitions or waiting for a signal transition are very useful when triggering a transition from within the application module. Another use case arises when attempting to trigger a state machine transition in a different application module. Registering and firing events are useful for this purpose.

Example Requirements

Example Requirements:

- Create a state machine with four state on the system clock domain

- Rename the states and perform the actions in the table below

| State Integer | State Name | Action |

|---|---|---|

| 0 | st_init | transition to st_start after 3.5 us |

| 1 | st_start |

set output pin 0 to logic '1' and wait for 1us

then transition to st_wait |

| 2 | st_wait |

set output pin 0 back to logic '0' and wait

wait for a signal named ' trigger ' to become logic 1 then transition to st_done |

| 3 | state_done | wait for 2 us then return back to st_init |

- Create a second state machine with two states on a 60MHz clock domain

- Do not rename the states . Leave them as integers

- Create a std_logic_vector signal named ' trigger '

- Drive the ' trigger ' signal to toggle from '0' to '1' and make the trigger signal logic '0' in state 0 and logic '1' in state 1

- Configure general purpose counter 0 to count 50us on the 60MHz clock domain and force the state machine into state 6 when the count is done.

| State Integer | State Name | Action |

|---|---|---|

| 0 | - |

set the 'trigger signal to logic '0'

transition to state 1 after 10 us |

| 1 | - |

set the 'trigger' signal to logic '1'

transition back to state 0 after another 10 us |

Note 1: The 'trigger' signal will be used to trigger the other state machine out of the st_wait state.

Note 2: The counter can trigger a state machine transition as long as the state machine is not scheduled to transition on that same clock cycle

Watch the Videos

Watch the Videos:

Tutorial lessons to be learned

Creating a state machine should be always

example

Reviewing the Commands

- "restart from scratch"

- "command"

- command"

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

- "command"

- "command"

- "command"

- "configure counter one

- "count ten"

- "ok".

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

Simulation Results

Simulation Results

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

VHDL Reference

VHDL Reference:

-

Completed Example:

<examle>.vhd

.

- API Syntax: < vhdl_call>

See Also

See Also

-

<

vhdl_call>

- Item 2

- Item 3

- Item 4

State Machine Timed Transtions

Overview

Overview:

State machine usage is extremely important in FPGA design in order to facilitate sequential operation. All of the procedure calls that SpeakHDL provides operate in parallels unless they are explicitly placed inside a state machine state. SpeakHDL makes it extremely easy to create state machines on any clock domain. States in SpeakHDL are of integer type. By using integer literal types, we can build state machine structures without needing a VHDL declaration statement.

There are three ways to trigger state machine state transitions:

- Transitions triggered by time

- Transitions triggered by signal change

- Transitions triggered by a registered event

Note: Time transitions and signal change transitions are used when programming within the same application module, whereas transitions based on an event can be triggered from between different application modules.

Example Requirements

Example Requirements:

Part One : Timed Transition and Signal Transition

- Create a file named state_machine_module.vhd

- Create a state machine with four state on the system clock domain

- Rename the states and perform the actions in the table below

| State Integer | State Name | Action |

|---|---|---|

| 0 | st_init | transition to st_start after 3.5 us |

| 1 | st_start |

set output pin 0 to logic '1' and wait for 1us

then transition to st_wait |

| 2 | st_wait |

set output pin 0 back to logic '0' and wait

wait for a signal named ' trigger ' to become logic 1 then transition to st_done |

| 3 | state_done | wait for 2 us then return back to st_init |

- Create a second state machine with two states on a 60MHz clock domain

- Do not rename the states . Leave them as integers

- Create a std_logic_vector signal named ' trigger '

- Drive the ' trigger ' signal to toggle from '0' to '1' and make the trigger signal logic '0' in state 0 and logic '1' in state 1

- Configure general purpose counter 0 to count 50us on the 60MHz clock domain and force the state machine into state 6 when the count is done.

| State Integer | State Name | Action |

|---|---|---|

| 0 | - |

set the 'trigger signal to logic '0'

transition to state 1 after 10 us |

| 1 | - |

set the 'trigger' signal to logic '1'

transition back to state 0 after another 10 us |

Lorem ipsum

Lorem ipsum

Part Two : Event Transition

- Create a new file named trigger_module.vhd .

- Remove the second state machine and delete the trigger signal

- Remove in the first state machine, remove the counter that sets a timeout

- In the first state machine, go to state 1 replace the signal by registering for event 0 to transition to st_done.

- Drive the ' trigger ' signal to toggle from '0' to '1' and make the trigger signal logic '0' in state 0 and logic '1' in state 1

| State Integer | State Name | Action |

|---|---|---|

| 0 | - |

set the 'trigger signal to logic '0'

transition to state 1 after 10 us |

| 1 | - |

set the 'trigger' signal to logic '1'

fire a event 0 and transition to state 0 when the event is acknowledged |

Watch the Videos

Watch the Videos:

Tutorial lessons to be learned

Creating a state machine should be always

example

Reviewing the Commands

- "restart from scratch"

- "command"

- command"

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

- "command"

- "command"

- "command"

- "configure counter one

- "count ten"

- "ok".

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

Simulation Results

Simulation Results

Lorem ipsum dolor sit amet, consectetur adipiscing elit, sed do eiusmod tempor incididunt ut labore et dolore magna aliqua. Ut enim ad minim veniam, quis nostrud exercitation ullamco laboris nisi ut aliquip ex ea commodo consequat.

VHDL Reference

VHDL Reference:

-

Completed Example:

<examle>.vhd

.

- API Syntax: < vhdl_call>

See Also

See Also

-

<

vhdl_call>

- Item 2

- Item 3

- Item 4