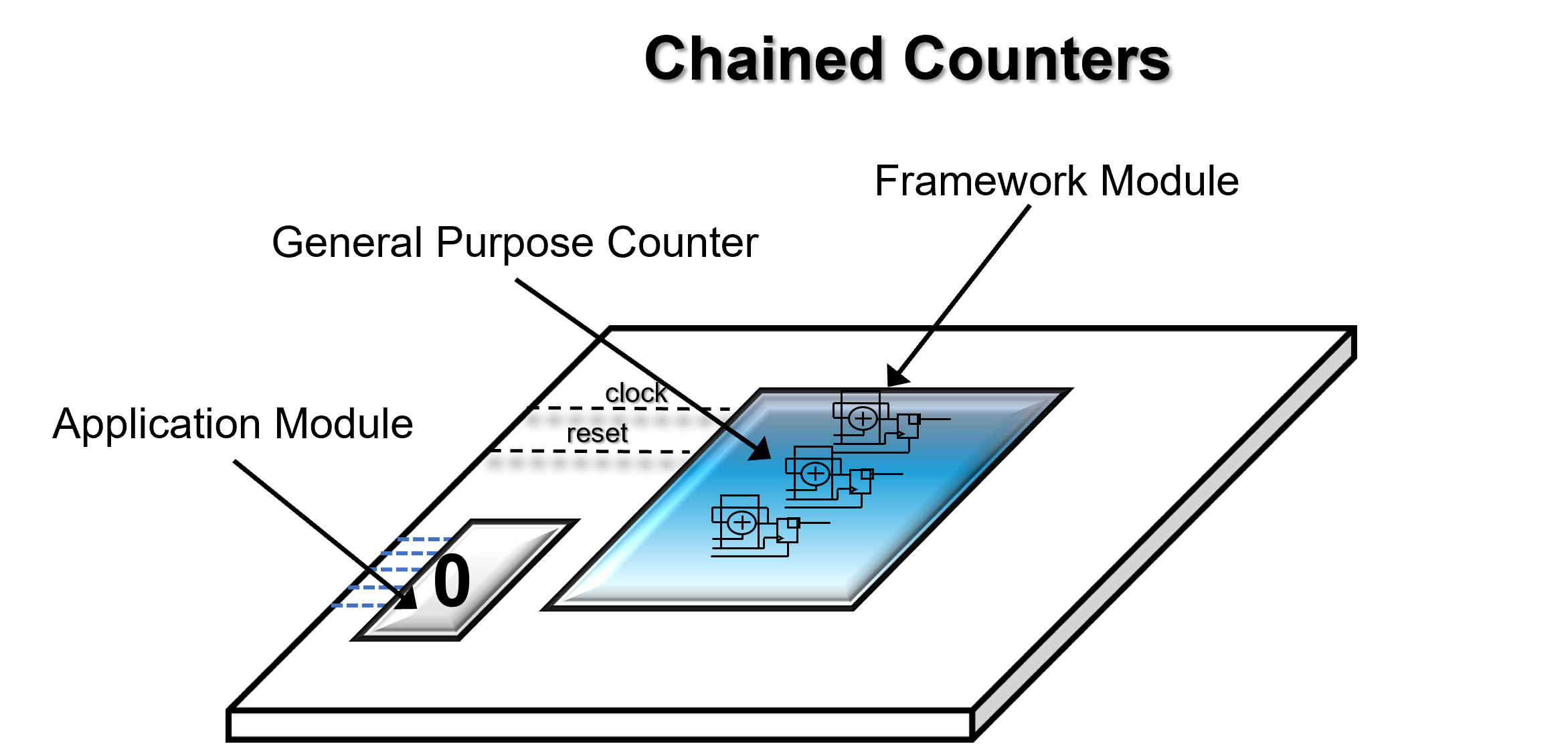

Chaining General Purpose Counters

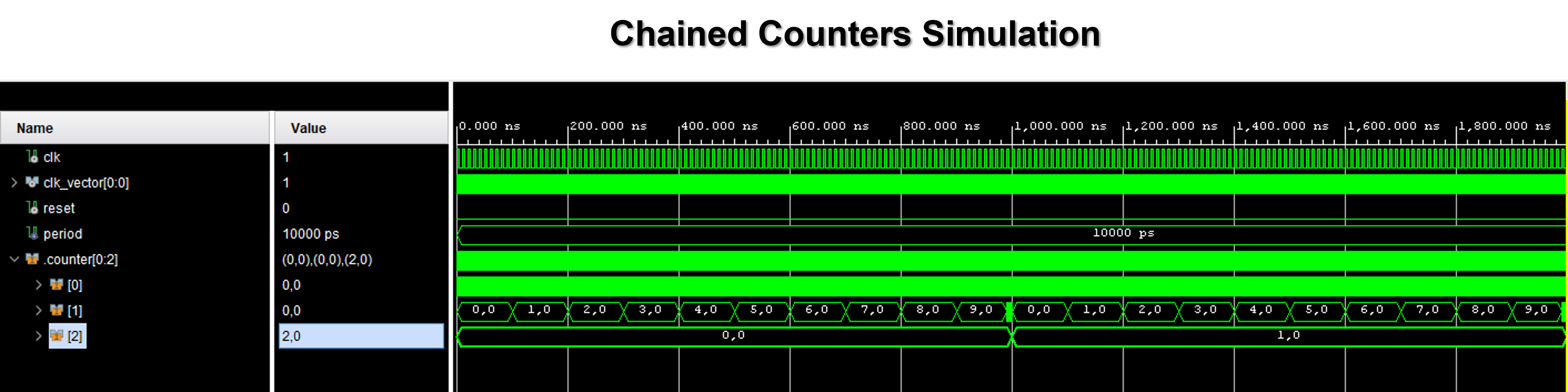

The following commands create three general purpose counters that all count to 10. The

done

signal of the lower indexed counters are used as the

enable

of the higher index counter.

Voice Commands

- "configure counter"

- "count ten"

- "configure counter one"

- "count ten"

- "enable chain"

- "configure counter two"

- "count 10"

- "enable chain"

- "ok"

Hotkey Commands

- cc

- count 10

- cc1

- count 10

- enable chain

- cc2

- count 10

- enable chain

- ok

Chaining General Purpose Counters

Chaining General Purpose Counters

- See also

- CONFIGURE_COUNTER

Chaining General Purpose Counters

Chaining General Purpose Counters

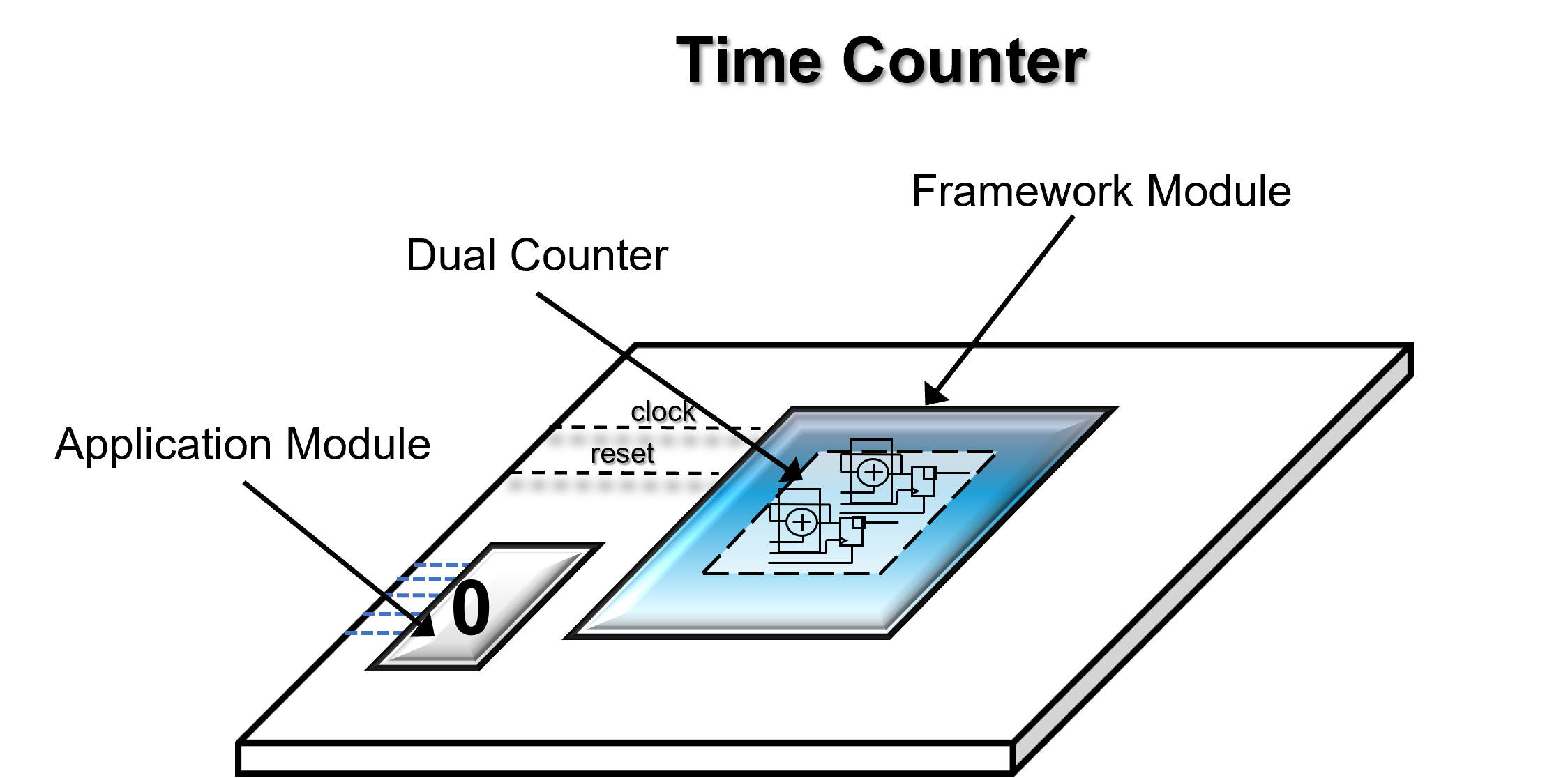

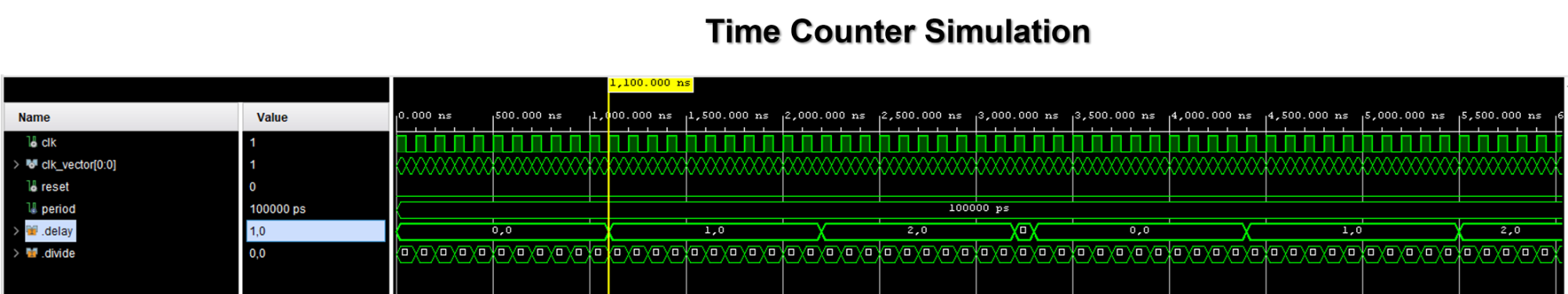

Creating A Time Counter

The following commands configure the divide counter (faster counter) to count 1.1us and the slower delay counter to count to 3. The net affect is a 3.3 us counter that rolls over and starts again, but outputs strobes every 1.1us. In order to cut down on simulation time, the clock frequency was dropped from 100MHz to 10MHz.

Voice Commands

- "time counter"

- "delay three"

- "divide one point one micro-second"

- "--"

- "ok"

Hotkey Commands

- tc

- delay 3

- divide 1.1us

- clk_freq = 10MHz

- ok

Creating A Time Counter

Creating A Time Counter

- See also

- time_counter_group

Creating A Time Counter

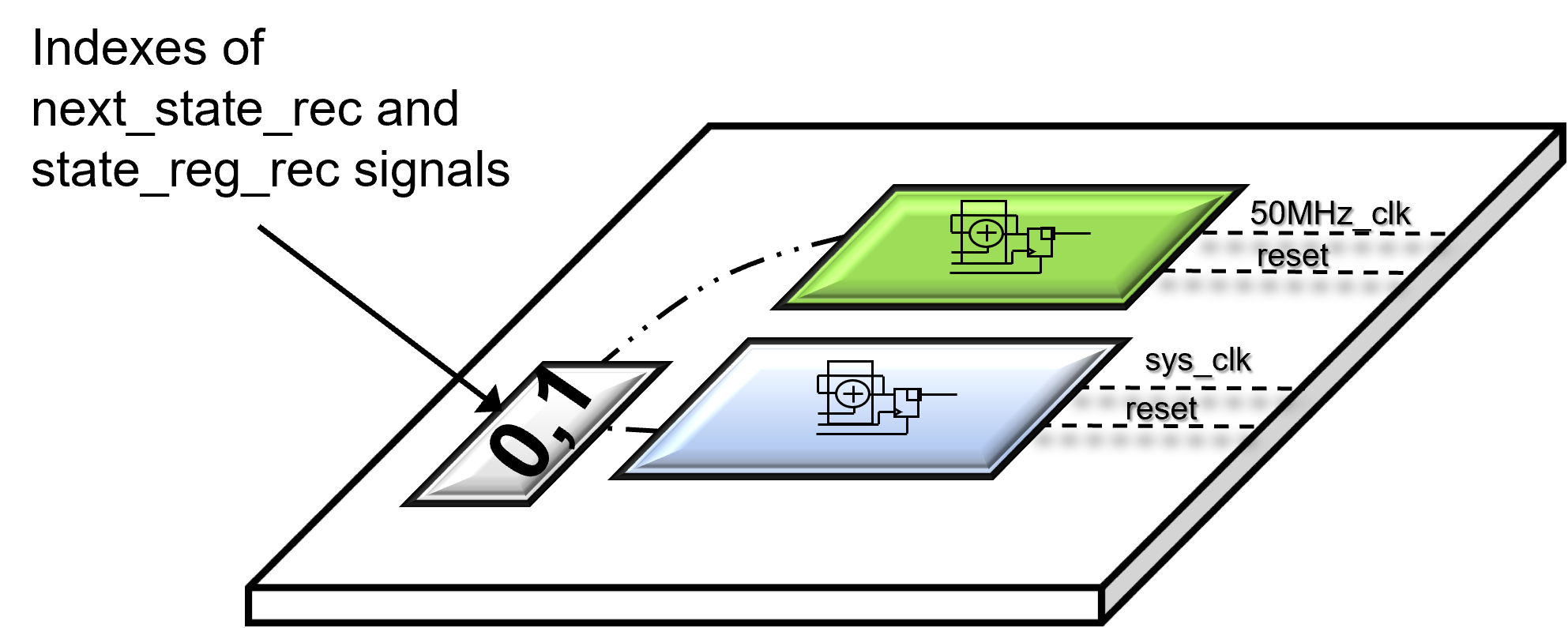

Multiple Clock Domain Counters

The following commands configure two framework counters. One counter operates on the default

sys_clk

domain (100MHz) while the other operates on a user specified 50MHz clock domain.

Voice Commands

- "resource zero"

- "configure counter zero"

- "resource one"

- "resource clock fifty mega-hertz"

- "configure counter zero"

Hotkey Commands

- rs0

- cc0

- rs1

- rs_clk 50e6

- cc0

Multiple Clock Domain Counters

Multiple Clock Domain Counters

- See also

- CONFIGURE_COUNTER

Multiple Clock Domain Counters

Multiple Clock Domain Counters

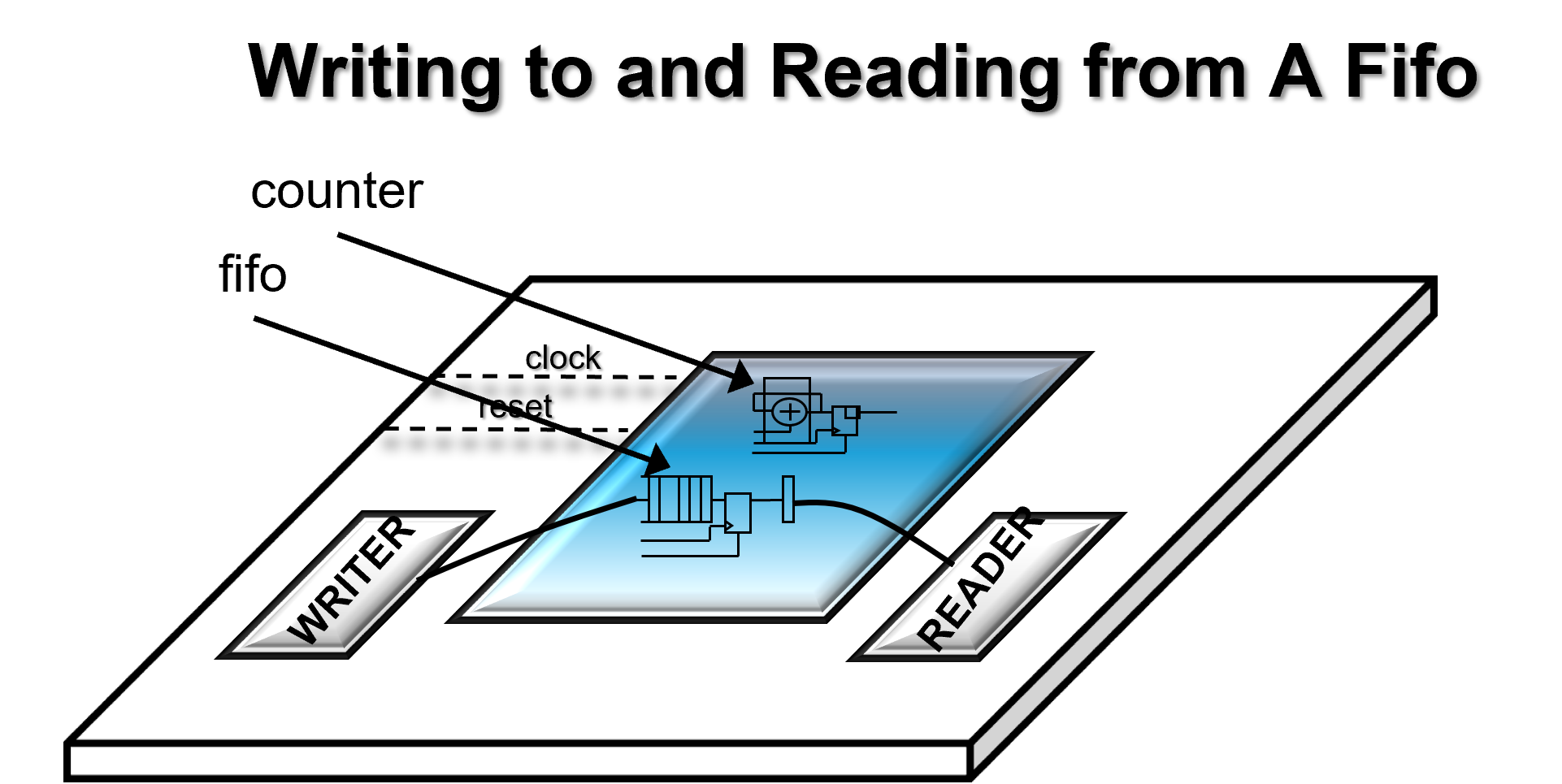

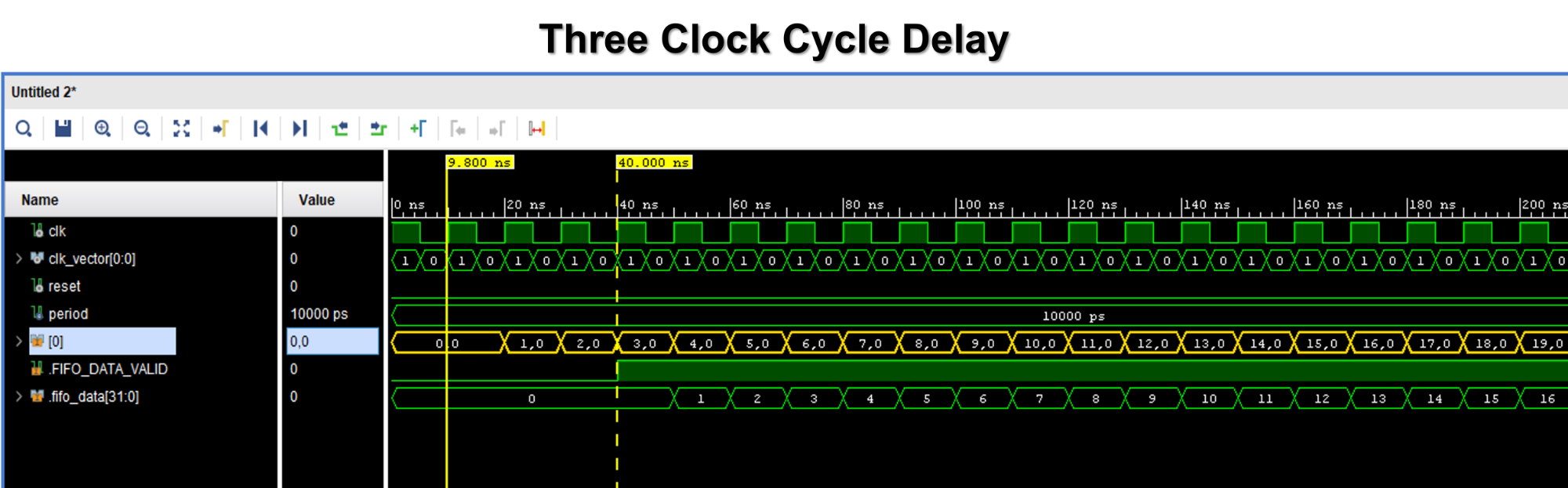

Writing to and Reading From a Fifo

Using the following commands, application module ' writer.vhd ' streams data from counter(0) into a fifo and application module ' reader.vhd ' reads the data from the fifo. Note that the fifo_write_enable signal is used as the enable for the counter.

writer.vhd Hotkey Commands

- cc

- enable .write_ready

- wr

- index reader

- data counter0

reader.vhd Hotkey commands

- rf

- index writer

Writing to and Reading From a Fifo

Writing to and Reading From a Fifo

Writing to and Reading From a Fifo

Writing to and Reading From a Fifo

- Note

- The WRITE_FIFO_DATA and the CONFIGURE_COUNTER procedure calls are operating in parallel, thus in this case it does not matter which call appears first in the VHDL code.

Writing to and Reading From a Fifo

- See also

- WRITE_FIFO_DATA

- READ_FIFO_DATA