Overview

With SpeakHDL, components and IP blocks are declared by copying and pasting a component declaration directly into the application module text file. When the 'ok' command is given, SpeakHDL automatically instantiates one component from the component declaration and automatically declares and connects signals to the component instance of the appropriate size and type based on the component declaration. When multiple instances of same component are instantiated, SpeakHDL automatically increments the component label numerically, however these components will share the automatically declared signal names. In this case, the developer is responsible for modification of the signal names of at least one component.

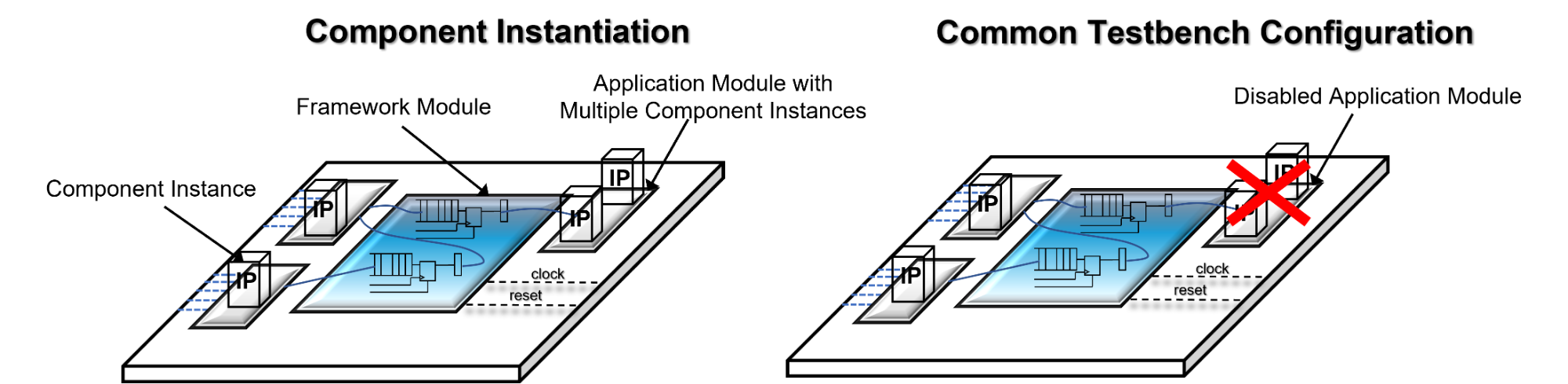

During simulation and synthesis, component instantiations are simulated and synthesized as part of the application module whereas all the interconnection hardware such counters, fifos and shared registers that get inferred by procedure call are simulated and synthesized as part of the framework module. The situation is subtle, but leads to a large productivity benefit during validation. When an application module is disabled, it is removed from the top level of the design which means that any components that have been instantiated inside the application module are also removed. Thus, a developer can save a substantial amount of development time by disabling some application modules and only simulating and synthesizing application modules with specific component instances. To maximize the benefit of performing incremental validation during testbench development, a developer may choose to instantiate only a single component inside an application module.

Example Component Declaration Syntax:

Copying and pasting the following component declaration, input_converter would result in SpeakHDL automatically instantiating the instance input_converter_0 shown below.

Declaration:

Instance:

In order to utilize a component by direct instantiation the user must make an entry into a local section of the config file. configuration_file.

Notes and Warnings

- Note

- 1) Components can be directly instantiated by referencing the component entity .vhd file inside the local section of the config file.

2) In order to directly instantiate a component, the .vhd filename must be located in the same directory as the application modules. If multiple components need to be instantiated, they should be added as a list component_filename = [<filename1>.vhd, <filename2>.vhd,...,<filenameN>.vhd ]. component_filename = [<filename1>.vhd, <filename2>.vhd,...,<filenameN>.vhd ].

- Warning

- 1) Multiple component are allowed to share the same input signals, however sharing the same output signals will cause a VHDL syntax error.

2) Direct Instantiation of components cannot currently be performed inside the SpeakHDL sandbox. This is due to the fact that the sandbox only writes, but does not read from the users local drive. Inside the sandbox, components must be declared by adding a VHDL component declaration into the application module.

- See also

- SIGNAL ASSIGNMENTS

- STATE MACHINE CONSTRUCTION

- AXI STREAM INTERFACE

- WRITE_FIFO_DATA

- READ_FIFO_DATA

- shared_register_group