Overview

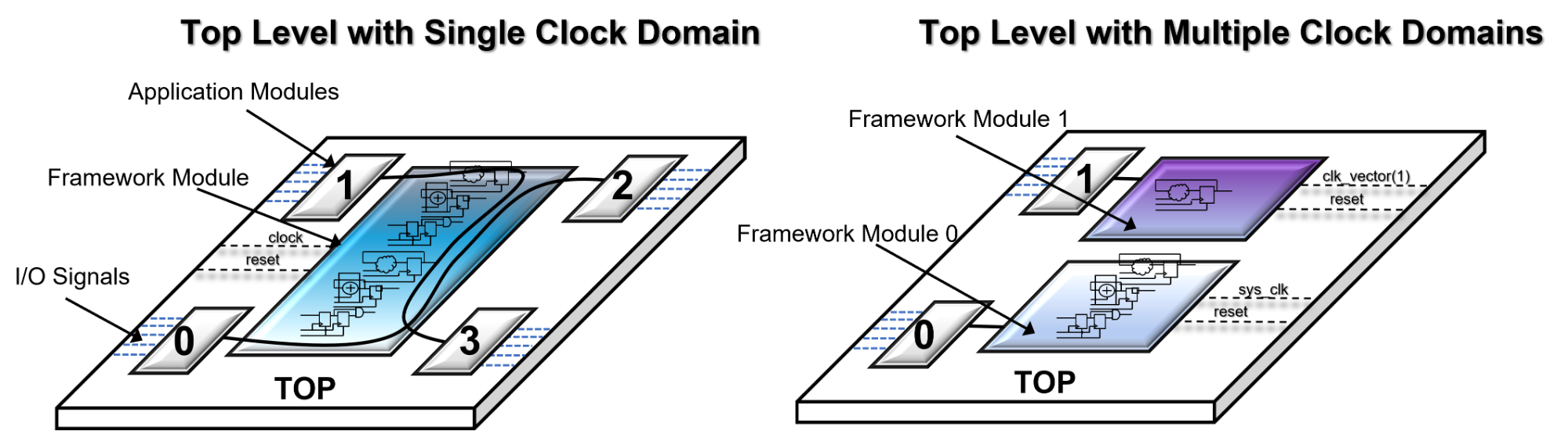

TOP.vhd is one of (4) auto-generated files that SpeakHDL creates or updates inside the top directory when the 'ok' command is given. It represents the top level of a FPGA design. However, when using a flat design architecture, the framework module and all application modules are always located at the top level of the hierarchy. Thus, with SpeakHDL, the top level of a design has much less significance than the top level in a traditional hierarchical architecture. When the 'ok' command is given, SpeakHDL indexes each application module, calculates the total number of I/O signals that are utilized by application modules, then auto-generates the top level design file. This is done by wiring up the next_state_rec and state_reg_rec array signals of each application module to corresponding portion of the framework module next_state_rec_array and state_reg_rec_array indexes.

The strategy is also generalized for the case of multiple framework modules that operate on multiple clock domains. To support multiple clock domains, the TOP.vhd file defines both a clk signal and a clk_vector signal where the clk signal is always the same as the sys_clk which is also equal to clk_vector(0). Higher indexes of the clock_vector signal will only be utilized by a framework module when the FPGA has multiple clock domains.

Example TOP.vhd File

Example Multiple Framework Module Instantiation

- Note

- 1) Disabled application modules do not get instantiated at the top level of the design.

2) The module index which is defined in USER_DEFS_PKG.vhd is passed to each application module from the top level by a VHDL generic constant.