Overview

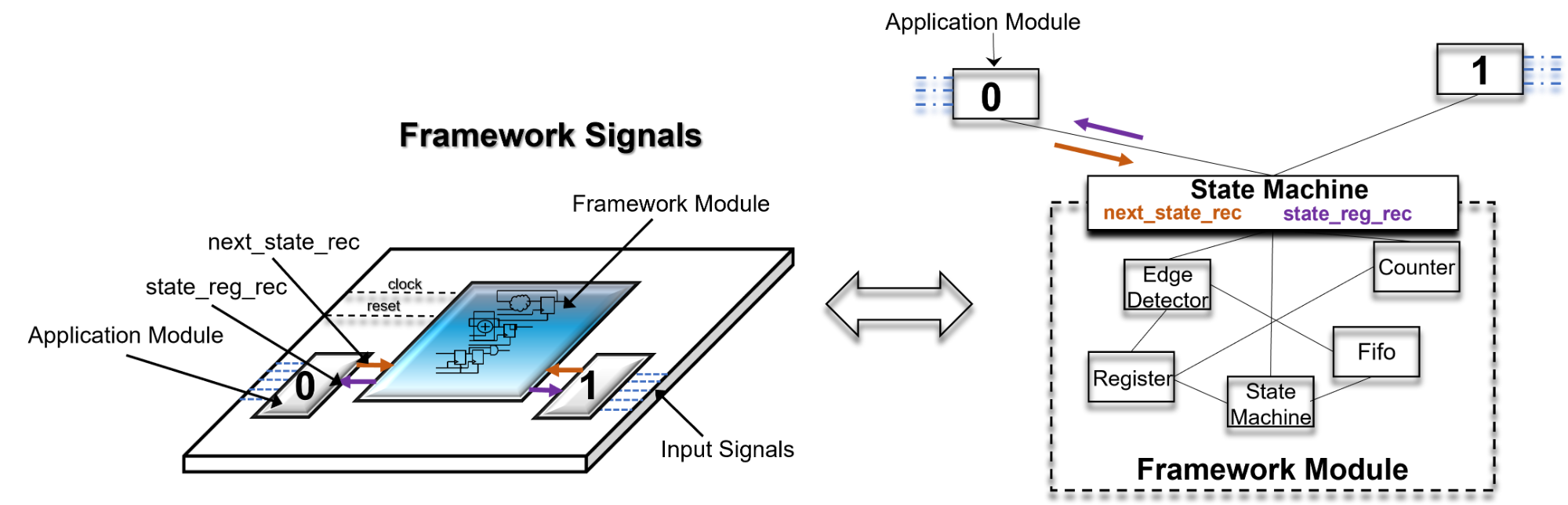

The next_state_rec signal is a VHDL data structure representing the combinatorial input value to a procedure call. Although the signal name ends with '_rec' which alludes to being a VHDL record type, the signal is actually an array of records. When making an API call, the next_state_rec represents the consolidation of all input parameters that are used to configure a framework resource. It should be noted that although the next_state_rec signal appears to be input parameter to an API procedure call, it is actually an output signal at the port interface of an application module. This means that the next_state_rec signal cannot be read by the application module. Because the signal cannot be read, during code development, it is of little interest to a developer.

The next_state_rec is always the next to last required parameter of an API call and is immediately followed by the state_reg_rec parameter. It should be noted that each index of next_state_rec and state_reg_rec can be placed either on the same clock domain or a separate clock domain by first by making a call to RESOURCE_SELECT and changing the resource clock frequency. Then any API calls made after the RESOURCE_SELECT procedure call will be made on the newly created resource domain and will be registered at that clock frequency.

Notes and Warnings

- Note

- 1) During synthesis, the next_state_rec signal is expected to synthesize to a large combinatorial multiplexer with the majority of its combinatorial I/O set to default.

Records | |

| NSR | |

| next_event_vec | NEV |

| next event vector record signal | |

| next_state_vec | NSV |

| next state vector record signal | |

| controlReq | std_logic_vector ( 0 to NUM_CONTROL_REQ_BITS- 1 ) |

| control request signal | |

| delayReq | DELAY_INTEGER |

| delay (slower) counter configuration | |

| delayEarlyReq | DELAY_INTEGER |

| delay (slower) counter early configuration | |

| divideReq | DIVIDE_INTEGER |

| divide(faster) counter configuration | |

| divideEarlyReq | DIVIDE_INTEGER |

| divide(faster) counter early configuration | |

| configCount | TRANS_COUNT_CFG_VEC_ARRAY |

| transition counter configuration | |

| configCountEarly | TRANS_COUNT_ARRAY |

| transition counter (early) configuration | |

| signalTransVec | CONDITIONAL_TRANSITION_ARRAY |

| conditioanl transition configuration | |

| exchangeRegisterReq | DX_VEC |

| low latency exhange register input data | |

| sharedRegisterReq | CX_VEC |

| shared register input data | |

| shift_left | DX_VEC |

| left shift register input data | |

| shift_right | DX_VEC |

| righ shift register input data | |