Overview

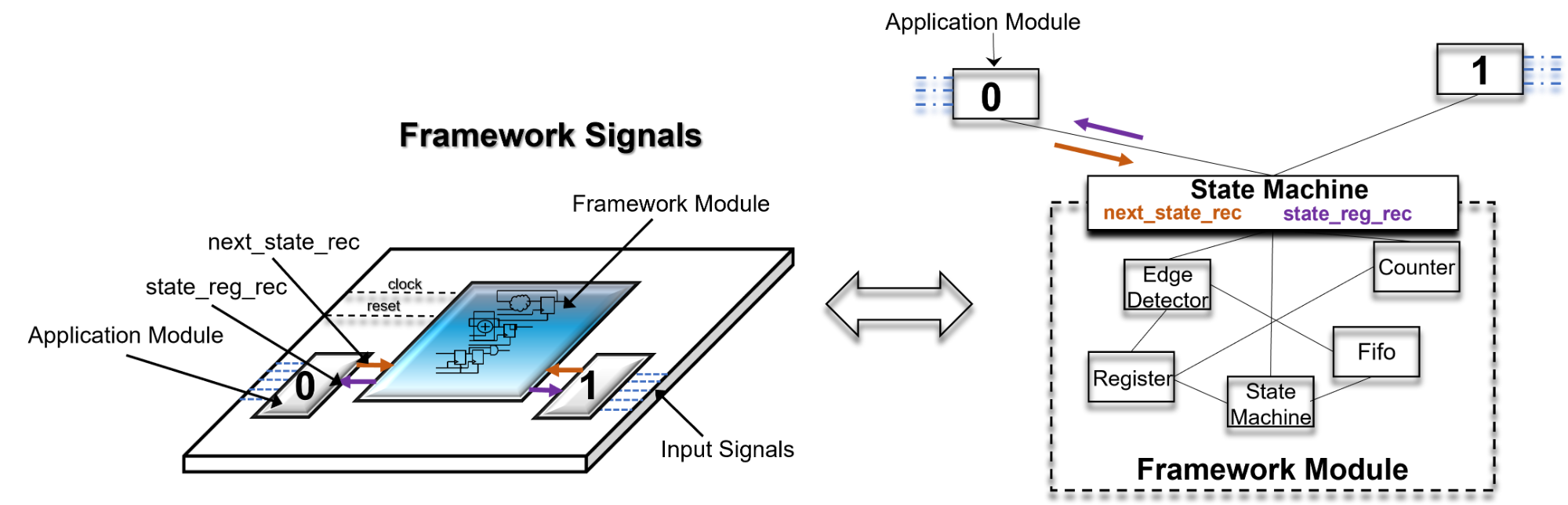

The state_reg_rec signal is a VHDL data structure representing the registered return value of a procedure call. Although the signal name ends with '_rec' which alludes to being a VHDL record type, the signal is actually an array of records. Each resource index of state_reg_rec is made up of approximately (20) VHDL record fields. SpeakHDL refers to the state_reg_rec record fields as framework signals which are used as inputs to application modules and represent a single framework resource that has been configured. Amongst other things, the state_reg_rec signal, contains data structures for hardware registers that include a single left and right shifter, a fifo, and a shared control register in addition to an array of counters, edge detectors, and event vectors, which can be indexed. These hardware registers are essentially 'pre-declared signals' that the developer can immediately utilize and that help facilitate productivity.

The state_reg_rec is always the last required parameter of an API call and appears immediately after the next_state_rec parameter. It should be noted that each index of the next_state_rec and state_reg_rec can be placed either on the same clock domain or a separate clock domain by first by making a call to RESOURCE_SELECT and changing the resource clock frequency. Then any API calls made after the RESOURCE_SELECT procedure call will be made on the newly created resource domain and will be registered at that clock frequency.

Notes and Warnings

- Note

- 1) During synthesis, the state_reg_rec signal is expected to synthesize to a large hardware register with the majority of its values unused by the application module.

2) Framework signals are the only record type data structure that SpeakHDL supports inside an application module. Framework signals are the only signals that can contain a '.' in the identifier name.

Records | |

| state_reg_rec | |

| The next_state_rec and state_reg_rec signals are required paramaters to every procedure call. | |

| index | INDEX_INTEGER |

| compile time integer index assigned to application module | |

| clk | std_logic |

| resource clock signal | |

| state_reg | STATE_INTEGER |

| current state register value (integer) range -1 to 14 | |

| counter | COUNT_ARRAY |

| array of records COUNT_REC record for counters consiting of .value and .done | |

| delay | COUNT_REC |

| delay (slower) counter record counter consiting of .value and .done | |

| divide | COUNT_REC |

| divide (faster) counter record counter consiting of .value and .done | |

| shared_register | std_logic_vector ( NUM_CONTROL_BITS- 1 downto 0 ) |

| register used to read/write control data | |

| FIFO_DATA_VALID | std_logic |

| fifo data valid signal | |

| fifo_data | std_logic_vector ( NUM_DATAX_BITS- 1 downto 0 ) |

| fifo data from fifo buffer (with flow control) | |

| FIFO_DATA_READY | std_logic |

| fifo data (read) ready signal | |

| FIFO_DATA_DONE | std_logic |

| fifo data (read) done strobe signal | |

| FIFO_WRITE_READY | std_logic |

| fifo write ready singal | |

| FIFO_WRITE_DONE | std_logic |

| fifo write done (usuually a strob) | |

| exchange_register | std_logic_vector ( NUM_DATAX_BITS- 1 downto 0 ) |

| low latency exchange register(no flow control) alternative to fifo_data | |

| shift_left | std_logic_vector ( NUM_DATAX_BITS- 1 downto 0 ) |

| left shift register | |

| shift_right | std_logic_vector ( NUM_DATAX_BITS- 1 downto 0 ) |

| right shift reguster | |

| rising_edge | std_logic_vector ( 0 to NUM_RISING_EDGE_DETECTS- 1 ) |

| array of rising edge detect 'strobes' | |

| falling_edge | std_logic_vector ( 0 to NUM_FALLING_EDGE_DETECTS- 1 ) |

| array of falling edge detect 'strobes' | |

| event_vector | std_logic_vector ( 0 to NUM_EVENTS- 1 ) |

| event vector signal | |

| status | std_logic_vector ( 0 to NUM_STATUS_BITS- 1 ) |

| status register | |

| fifo | FIFO_REC |

| fifo record signal showing fifo flags and element counters (primarialy used during debug) | |

| EXT | EXT_REC |

| exterior control data be passed into the framework (used during tests modes) | |