Overview

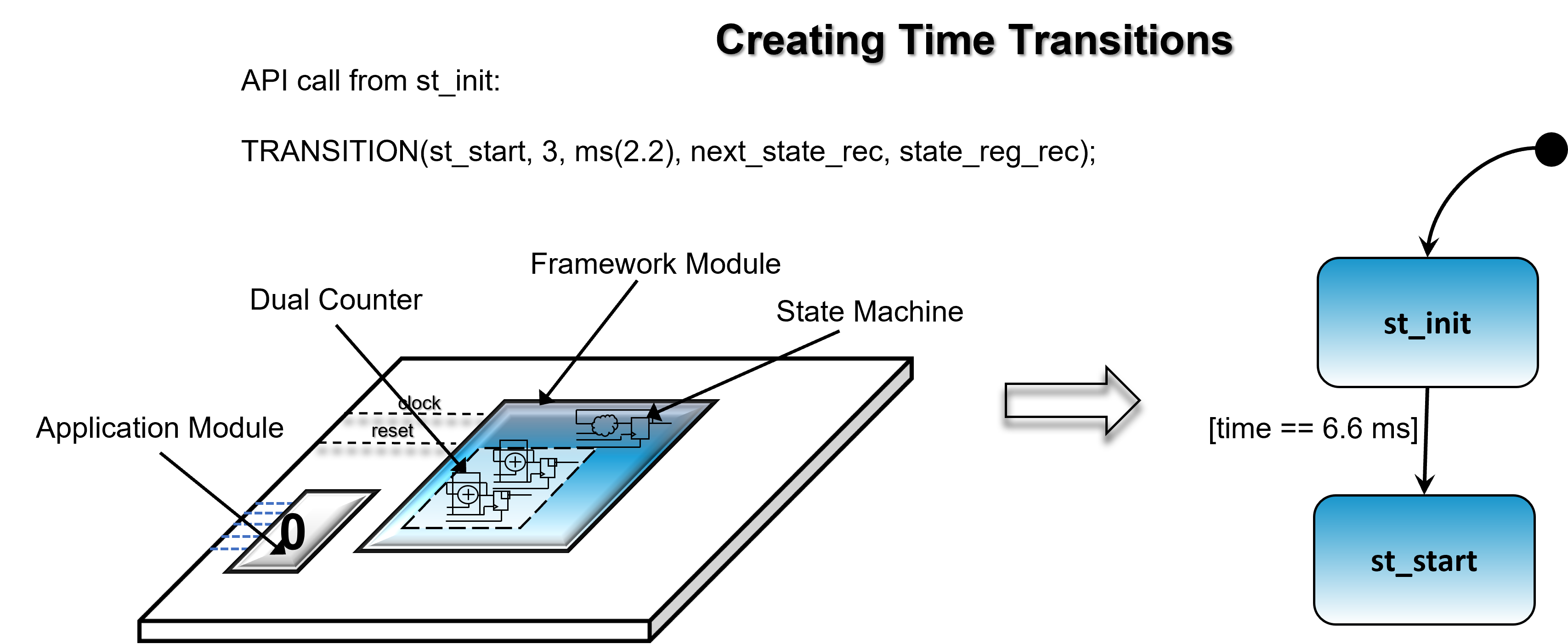

The TRANSITION procedure call schedules a state machine transition to occur after a specified time duration. To achieve a timed transition, a dual hardware counter is used as a state_timer by configuring the counter to increment every clock cycle. The user specifies the desired state of the transition and the number of clock cycles that the hardware counter should count before rolling over and triggering the transition. The timer_count value can be specified as either a constant integer or a timing function, us(), ms(), or sec() that evaluates to a constant integer. When a timing function is used, the number of clock cycles that the hardware counter counts before a transition is calculated based on the clock domain frequency.

By default, the TRANSITION procedure call schedules a state transition on the first time the dual hardware counter rolls over. However, an optional integer argument can be passed as the last parameter. This state_timer_iteration value indicates the number of times the state_timer should roll over before a transition occurs. One clock cycle before a transition occurs, both the state_timer.done and state_timer_iteration.done signals will be asserted for one clock cycle, and state_reg_rec(N).state_reg will transition its value on the next rising edge of the clock.

It should be noted that the dual hardware counter used to implement the state_timer and state_timer_iteration has no explicit reset mechanism. Once configured, by the TRANSITION procedure call, the state_timer and state_timer_iteration values can only be reset due to a state transition. If pausing or explict reset capabilities are needed for the developer should utilize CONFIGURE_COUNTER procedure call to configure a general purpose counter which gives more flexibility.

Usage Example

- Todo:

- Add Example Usage and image of state machine

Example API Call(s):

TRANSITION( st_start, 1, next_state_rec, state_reg_rec );

TRANSITION( 2, ms(1), next_state_rec, state_reg_rec, 5 );

Call Data [ 5 parameters (4 mandatory) ]

- Parameters

-

[in] transition_state [1] integer state to transition to when delay_done asserted [in] timer_count [2] integer state timer value (minus one) before rollover [out] next_state_rec [3] [in] state_reg_rec [4] [in] num_iterations* [5] (optional) integer state timer iteration value (minus one) before rollover

Return Data

- Parameters

-

[in] state_reg_rec(M).state_timer.value [1] [integer] state timer count value returned from framework

[in] state_reg_rec(M).state_timer.done [2] [std_logic] strobe asserted '1' before rollover [in] state_reg_rec(M).state_timer_iteration.value [3] [integer] state timer iteration count value returned from framework [in] state_reg_rec(M).state_timer_iteration.done [4] [std_logic] strobe asserted '1' before rollover

Command Reference

Voice and Hotkey Commands:

- See also

- Transition Commands

Command Parameter Mapping

- Parameters

-

[in] transition_state [1] "go to [state] (<state>|<integer>)" [in] state_timer [2] "timer <integer>" [out] next_state_rec [3] [in] state_reg_rec [4] [in] state_timer_iteration [5] "iteration <integer>"

Command Return Data

- Parameters

-

[in] state_reg_rec(M).state_timer.value [1] [integer] "state timer value" [in] state_reg_rec(M).state_timer.done [2] [std_logic] "state timer (done|strobe)" [in] state_reg_rec(M).state_timer_iteration.value [3] [integer] "iteration value" [in] state_reg_rec(M).state_timer_iteration.done [4] [std_logic] "iteration (done|strobe)"

Voice/HotKey Command Sequence

TRANSITION( 4, ms(1), next_state_rec, state_reg_rec, 10 );

| Voice Command | HotKey Sequence |

|---|---|

| "transition to state four" | tr4 |

| "count one millisecond" | count 1ms |

| "iteration ten" | iteration 10 |

Notes and Warnings

- Note

- The minimum time duration before a transition can occur is 1 clock cycle.

- A valid state must be a non-negative integer literal or a VHDL constant integer state name prefixed by 'st_'. If the transition_state value is given as the constant -1, then no transition will occur.

- Utilizing a state_timer over a general purpose counter when appropriate provides better semantics and reduces debugging time due to the fact that the state_timer is guaranteed to be reset back to zero upon a transition.

Procedures | |

| TRANSITION( transition_state: STATE_INTEGER timer_count: in integer signal next_state_rec: out NSR state_reg_rec: in SRR num_iterations: in integer 1 ) | |

| TRANSITION( transition_state: STATE_INTEGER timer_count: in integer signal next_state_rec: out NSR_ARRAY state_reg_rec: in SRR_ARRAY num_iterations: in integer 1 ) | |

| Overloaded for array interface. | |