Overview

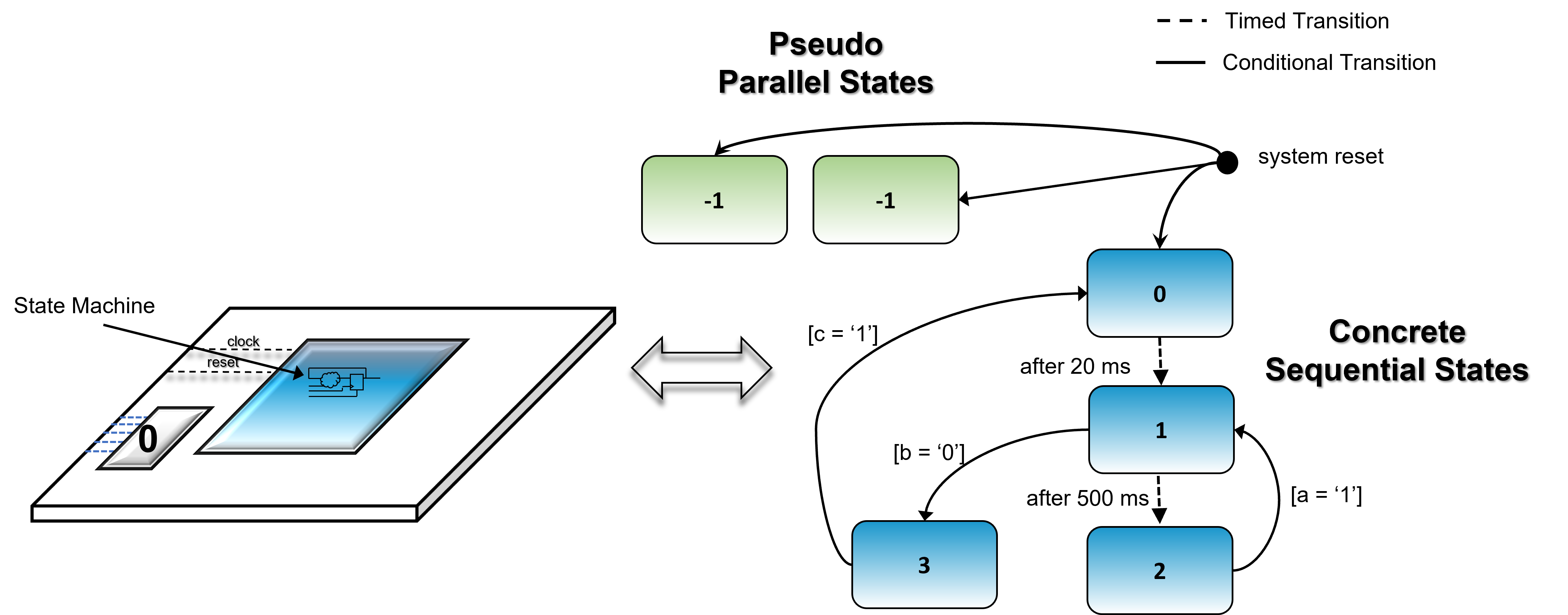

Controlling the order of operations is essential to any application. For FPGA development, sequential operations are almost always implemented through the use of a state machine, whether it be implicit or explicit. Thus, SpeakHDL makes it very easy to construct state machines and to create timed transitions and conditional transitions. With SpeakHDL, the state register was chosen to be of type integer instead of a user defined type for several reasons:

- Sequential operations can use the notion of counting which makes intuitive sense.

- Upon reset a state machine can be defined to intuitively startup in state 0.

- States can take the value of integer literals which need not declared.

- The notion of a 'parallel' state, or a states operating concurrently can be generalized to operate in pseudo-state, state -1.

With SpeakHDL, the input and output relationship of all procedure calls is implemented as a state machine. By defining non-negative integers values a concrete states, where operations are performed sequentially, and integer negative one as a pseudo-state, where operation are performed in parallel, there is now very little distinction between procedure calls that perform operations sequentially and those that operate in parallel. Conceptually, the only distinction is the context in which the next state logic is considered valid.

As an added benefit, when constructing a state machine, such a notion of state -1 is also intuitive. Procedures that operate in parallel would be located outside the VHDL case construct, just above state 0 while procedures operating sequentially would be placed inside the respective concrete state. The code below shows the VHDL procedure call implementation of state diagram. Note how timing functions are used to within the TRANSITION procedure call to calculate the number of clock cycles before a transition. Also of interest, is how SpeakHDL handles the concept of a time-out. In state 1, both the TRANSITION and CONDITIONAL_TRANSITION procedure calls are used. The semantics is such that if 500 ms occurs before b = '0', then the timed transition wins over the conditional transition. In the rare occurrence that the time-out expires and b = '0' occurs in the same clock cycle, then the conditional transition wins. This due to the fact that SpeakHDL designates conditional transitions to have priority over timed transitions by placing CONDITIONAL_TRANSITION under TRANSITION within the same state.

Constructing State Machines

In SpeakHDL a state machine is constructed by either the voice command "configure state machine" or the hotkey sequence sm. Any application module can construct any number of state machine simply by placing the newly created state machine on a separate resource domain. For convince SpeakHDL allows for an optional resource index to be placed after the command in order to create a state machine on another resource index. For example, the sequence of commands sm, sm1, sm2 would construct (3)

Renaming States and the 'st' Prefix

Statemachine states can be renamed from the default integer literals in one of two ways. Either by:

- using the name hokey sequence command followed by a list of state names

- typing a valid VHDL identifier in place of the integer literal directly in the text editor then giving the 'ok' command

When a state is renamed, SpeakHDL, automatically creates a constant integer declaration and ensures that the name of state is prefixed by st_. SpeakHDL uses the st_ convention to prefix constant integers that are used as states. This ensures that user defined state names will never collide with VHDL keywords. For example, creating a state called wait would cause a VHDL syntax error, however st_wait is an allowable state declaration.

Command Reference

Voice and Hotkey Commands:

Notes and Warnings

- Note

- 1) Each state machine is allowed to define up to 15 states in the range of 0 to 14.

2) The state machine framework signal is state_reg_rec(N).state_reg and is typically globally aliased to state_reg for resource 0.