Overview

With SpeakHDL, signal assignments must be made with a VHDL when-else statement and must be placed outside of a process construct. These constraints placed on signal assignments are by design and are part of the productivity strategy to separate combinatorial logic from registered logic. When-else signal assignments are not nearly as flexable as signal assignments that could be made inside a process using a if-then-else statement. However, SpeakHDL does not allow 'if-then-else' statements. It is the lack of flexibility which makes the when-else statement less prone to the abuse and ultimately much easier to debug during simulation.

For SpeakHDL, the when-else construct is flexible enough to model (3) of the most interesting signal assignment use cases including:

- modeling of a simple wire a <= '1';

- modeling of multiplexed combinatorial signals a <= '1' when (reset = '1') else'0' when (state_reg = st_wait) elseb;

- modeling multiplexed registered signals a <= '1' when state_reg = st_init else'0' (when b = '1') and rising_edge(clk);

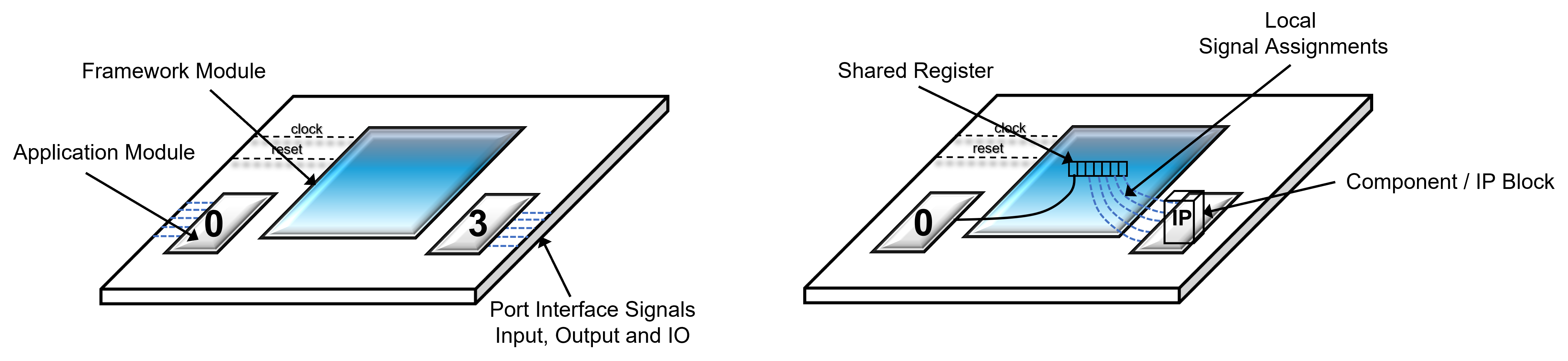

Declarations for I\O and Local Signals

SpeakHDL automatically creates a declaration for both I\O and local signals when a signal assignment is made. Because SpeakHDL only attempts to resolve VHDL std_logic, std_logic_vector and integer data types, it is possible to incorporate a reasonable number conventions into the command syntax to automatically create a signal declaration. In general, hotkey sequences for I\O signals follow the same command syntax for a local signal declaration. However, there are a few important differences:

1) Local signals can be of integer but I\O signals must be either std_logic or std_logic_vector.

2) Commands for I\O signal must be preceded with a keyword input, output or io.

3) Users must define FPGA pin location for an I/O signal.

4) Declaration aliases for I\O signals are handled as alias entries in the config file whereas local signals are handled as normal VHDL signal declarations.

Command Syntax for Signal Assignments

SpeakHDL follows the following command conventions when declaring and selection of signals depending on their type. If the VHDL identifier does not exist when the sequence is made, SpeakHDL makes a declaration and a selection of the signal. Otherwise, SpeakHDL makes a selection.

| VHDL TYPE | HOTKEY COMMAND SYNTAX | EXAMPLE | AUTOMATIC DECLARATION |

|---|---|---|---|

| std_logic | valid VHDL identifier followed by semicolon | sim_card_en; | signal sim_card_en : std_logic; |

| std_logic_vector | valid VHDL identifier followed by downto range | data_vector(7 downto 0) | signal data_vector : std_logic_vector(7 downto 0); |

| std_logic_vector | valid VHDL identifier followed by shorthand range | data_vector7:3 | signal data_vector : std_logic_vector(7 downto 3); |

| integer | valid VHDL identifier with suffix _i | edge_count_i | signal edge_count_i: integer; |

Command Reference

Voice and Hotkey Commands:

- See also

- Signal Assignments Commands

Notes and Warnings

- Note

- 1) The trailing semicolon is required when declaring or selecting the std_logic type, but is optional for declaring the std_logic_vector or integer types.

2) In SpeakHDL, the when-else statement and the CONDITIONAL_TRANSITION procedure call make up the only 2 ways to infer conditional branching of data flow.

- Warning

- 1) A when-else signal assignment that involves a conditional with no else logic will result in a register being inferred for that signal.

2) Declaring an input, output or io signal without a corresponding pin assignment will result in an error or warning when the 'ok' command is given.

3) Attempting to declare a signal that resembles a framework variable i.e. counter_value_i could result in an erroneous signal assignment.