Overview

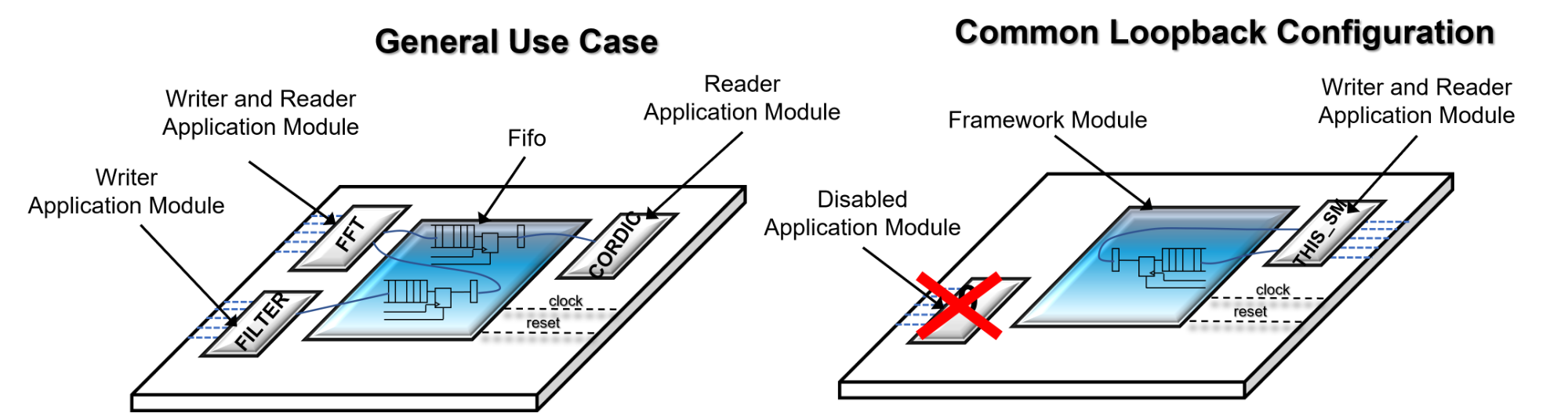

The WRITE_FIFO_DATA procedure call sets up a channel for point to point data to be sent to another application module. The data could be transferred either using to a read buffer which uses flow control, or as simple registered data through the framework module. The data is said to be point to point because the caller of WRITE_FIFO_DATA must reference the specific application module intended to be the reader. In addition, the application module intended to be the reader must utilize the READ_FIFO_DATA procedure call and reference the specific writer application module in order to accept the data. In general, application modules reference one another by VHDL entity name. However, when an application module references itself (when looping back data), that application module must refer to itself as this_module and not by its own entity name.

Multiple Channel Setup

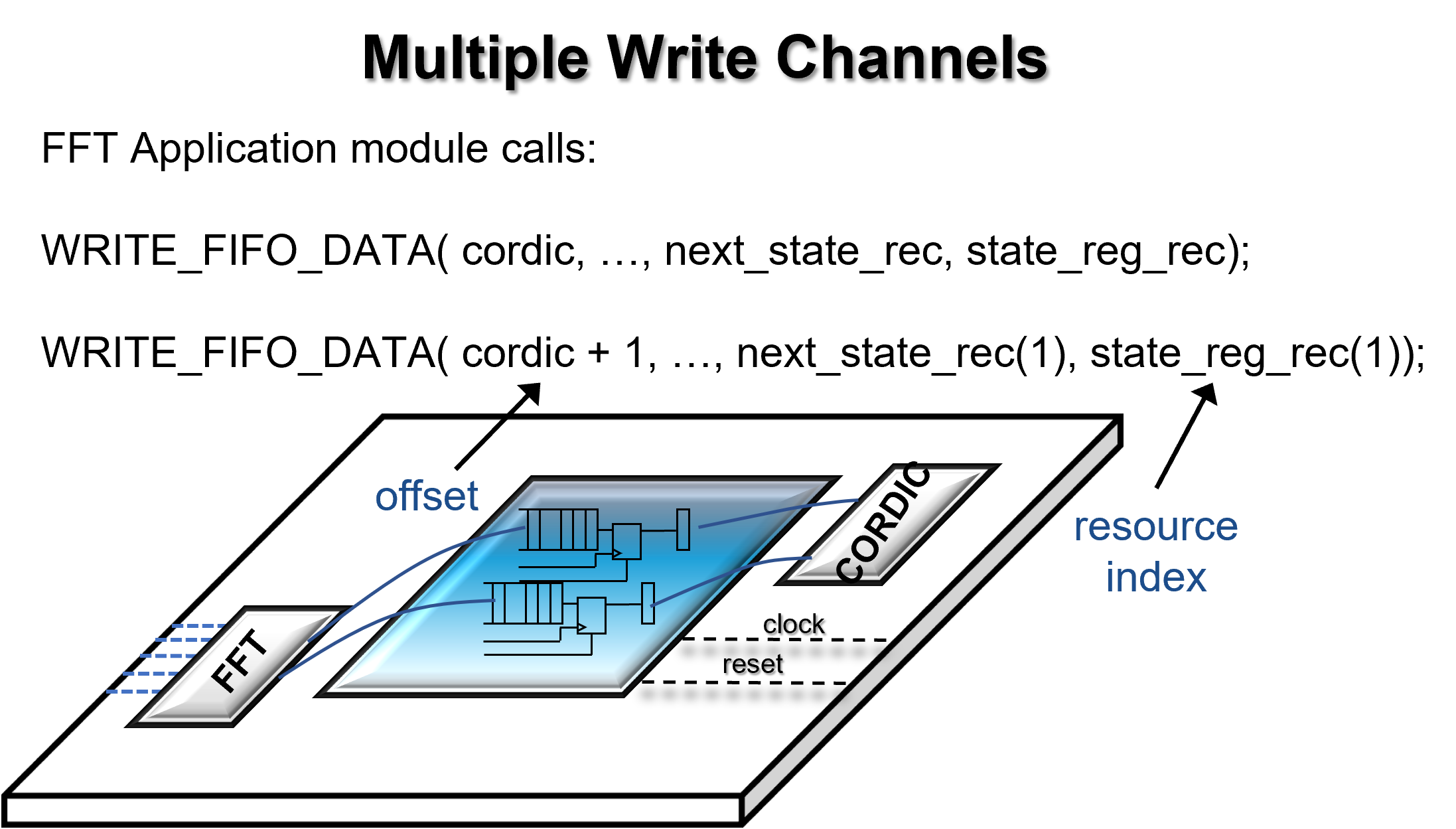

Each application module is allowed to set up any number of point to point channels. To set up multiple write channels, an application module makes multiple calls to WRITE_FIFO_DATA, each on a different resource index,

(M). Before compile time, each application modules entity name is mapped to as a constant integer value that specifies the starting resource index assigned to that application module. Thus, it is possible to write to two or more data channels intended for an application module simply by adding an offset number to the intended reader application module entity name.

- Note

- The application module that calls WRITE_FIFO_DATA only sets up a channel but does not allocate fifo buffer. It is the application module calling READ_FIFO_DATA which actually 'owns' the fifo hardware and specifies the fifo depth for the channel. This also means that the caller of WRITE_FIFO_DATA cannot reset the fifo buffer. Only the application module that calls READ_FIFO_DATA can reset the fifo buffer by calling RESET_FIFO.

Operation

When the WRITE_FIFO_DATA procedure call is made, the writer application module waits for the state_reg_rec(M).fifo_write_ready signal to become logic '1' indicating that the fifo is not full, then transfers the data_in signal value through a framework fifo when the state_reg_rec(M).fifo_data_valid signal is asserted to logic '1'. Valid data is available on the receive side of the fifo buffer after 3 clock cycles on the state_reg_rec(M).fifo_data_reg register.

If no flow control is necessary, registered point to point data can still be sent using the WRITE_FIFO_DATA and received using the READ_FIFO_DATA procedure calls. This data will be always available from the writer application module on the state_reg_rec(M).exchange_reg register 1 clock cycle after it is written regardless if state_reg_rec(M).fifo_data_valid is asserted or not. This allows the READ_FIFO_DATA procedure call to be utilized receive both buffered data (with flow control) and low latency registered data (with no flow control) with the same API calls.

The maximum data width that can be transferred by the WRITE_FIFO_DATA call is set by data_width in the config_file. Thus, any input data placed on data_in must be less than or equal to data_width bits with Most Significant Bit (MSB) assumed to be leftmost bit of the input data. All data bits on the left of the MSB will be set to '0' by default or will be set to the value of the MSB if the WRITE_FIFO_DATA optional parameter is set to SIGN_EXTEND.

In addition, the caller of WRITE_FIFO_DATA can specify a non-negative NUM_ELEMENTS to write to the fifo buffer, and optionally a non-negative transition_state to schedule a state machine transition to when the number of requested elements have been sent. If both NUM_ELEMENTS and transition_state are set to the value -1, then the fifo is configured to be a streaming write fifo.

Usage Example

Writing to and Reading from a Fifo

Example API Call(s):

WRITE_FIFO_DATA( reader, srr.counter(0).value, srr.fifo_write_ready, -1, -1, next_state_rec, state_reg_rec );

Call Data [ 8 parameters (7 mandatory, 1 optional) ]

- Parameters

-

[in] sm_index [1] name/offset index of the receiving application module resource or this_module for loopback [in] data_in [2] data to be sent to the destination buffer [in] data_valid [3] valid signal to be asserted to logic '1' when the data is valid [in] NUM_ELEMENTS [4] number of elements to be written to the buffer (-1 indicates streaming) [in] transition_state [5] integer state to transition to when NUM_ELEMENTS are written [out] next_state_rec [6] [in] state_reg_rec [7] [in] bit_option* [8] optional (ZERO_PAD|SIGN_EXTEND|REVERSE_BITS) default ZERO_PAD

Return Data

- Parameters

-

[in] state_reg_rec(M).FIFO_WRITE_READY [1] [std_logic] status value to be monitored by writer before writing attempting to write data [in] state_reg_rec(M).FIFO_WRITE_COUNT [2] [integer] number of data that has been written (should not need to be used directly) [in] state_reg_rec(M).FIFO_WRITE_DONE [3] [std_logic] status signal that indicates whether the write has completed (should not need to be used directly)

Command Reference

Voice and Hotkey Commands:

- See also

- Write Fifo Data Commands

Command Parameter Mapping

- Parameters

-

[in] sm_index [1] "(write | stream) [to] <module_integer_name>" [in] data_in [2] "data <fifo_input_data>" [in] data_valid [3] "(enable | [data] valid) <std_logic>" [in] NUM_ELEMENTS [4] "count <integer>" [in] transition_state [5] "go to [state] (<state>|<integer>)" [out] next_state_rec [6] [in] state_reg_rec [7] [in] bit_option* [8] "sign extend"

Command Return Data

- Parameters

-

[in] state_reg_rec(M).FIFO_WRITE_READY [1] [std_logic] "write ready" [in] state_reg_rec(M).FIFO_WRITE_COUNT [2] [integer] "write count" [in] state_reg_rec(M).FIFO_WRITE_DONE [3] [std_logic] "write done "

Voice/HotKey Command Sequence

WRITE_FIFO_DATA( this_module, input_data, input_valid, 128, st_data_done, next_state_rec, state_reg_rec );

| Voice Command | HotKey Sequence |

|---|---|

| "write_fifo_data" | wf |

| "data input data" | data input_data |

| "enable input valid" | enable input_valid |

| "count one twenty eight" | count 128 |

| "goto state data done" | goto data_done |

Notes and Warnings

- Note

- 1) The data_in parameter is overloaded to accept std_logic_vector, std_logic_vector_array, integer, or integer_array data types.

2) Integer types from counters or data_files can be very useful for sending test data vectors to fifos to validate connectivity between application modules.

3) Streaming fifos use slightly less framework resources because the fifo does not need to utilize a counter for handling the element count and does not need to schedule a state machine transition.

- Warning

- Attempting to write data with larger than data_width number of bits will lead to a VHDL compile error.

Procedures | |

| WRITE_FIFO_DATA( sm_index: in integer data_in: std_logic_vector data_valid: in std_logic NUM_ELEMENTS: integer transition_state: integer signal next_state_rec: out NSR state_reg_rec: in SRR BIT_OPTION: BIT_OPTION_TYPE ZERO_PAD ) | |

| WRITE_FIFO_DATA( sm_index: in integer data_in: std_logic_vector data_valid: in std_logic NUM_ELEMENTS: integer transition_state: integer signal next_state_rec: out NSR_ARRAY state_reg_rec: in SRR_ARRAY BIT_OPTION: BIT_OPTION_TYPE ZERO_PAD ) | |

| 0verloaded for array next_state_rec and state_reg_rec. data_in and sm_index overloaded for types integer, std_logic_vector. | |