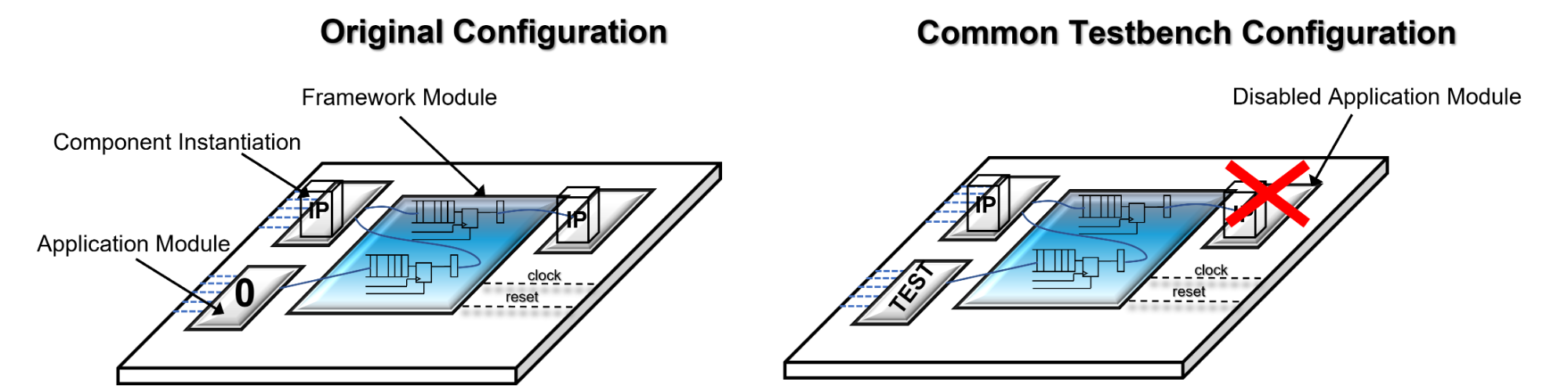

Overview

The DISABLE_FILE procedure call is offered as a convenience function that can be used to disable an application module from being active during simulation and synthesis. When the DISABLE_FILE procedure call is present in a .vhd file, SpeakHDL:

1) Sets the application module's module_index to -1 inside the USER_DEFS_PKG.vhd file.

2) Excludes the application module's files contents when calculating the amount of resources that get added to the framework module.

3) Excludes the application module's VHDL entity from being added to the TOP.vhd file.

In addition, the following architecture definition is added to the bottom of the .vhd file:

This statement above adds an empty VHDL architecture named 'disabled' to the current entity that will be analyzed last by the simulation/synthesis tool. The net effect is to ignore all the application module logic while keeping the actual .vhd file intact. This can be convenient when designing a testbench for validation. Disabling any non-essential application modules can substantially speed up debugging time while simultaneously cutting down on simulation time. The situation is even more pronounced when a component is instantiated inside an application module. In this case, using DISABLE_FILE will also serve to disable the component from being simulated or synthesized.

Example API Call(s):

DISABLE_FILE(next_state_rec, state_reg_rec);

Call Data [ 2 parameters (2 mandatory) ]

- Parameters

-

[in] next_state_rec [1] [in] state_reg_rec [2]

Return Data

None

Command Reference

Voice and Hotkey Commands:

Command Parameter Mapping

None

Command Return Data

None

Voice/HotKey Command Sequence

DISABLE_FILE(next_state_rec, state_reg_rec );

| Voice Command | HotKey Sequence |

|---|---|

| "disable file" | disable file |

Usage Example

- Todo:

- Add Example Usage

Notes and Warnings

- Note

- 1) Setting an application module to disabled does not affect the local contents of the configuration file.

2) Enabled and disabled application module information can be viewed in the ok.log file.

Procedures | |

| DISABLE_FILE( signal next_state_rec: out NSR , state_reg_rec: in SRR ) | |

| DISABLE_FILE( signal next_state_rec: out NSR_ARRAY , state_reg_rec: in SRR_ARRAY ) | |

| Overloaded for array interface. | |